# **TangerineSDR**

# **TangerineSDR**

# RF Receiver Module (RFM-5001D)

# **Interface Control Document**

Version Number: 0.7

Version Date: December 18, 2020

Document Number: TSDR-RFM-5001D-ICD

# **VERSION HISTORY**

| Version<br>Number | Implemented<br>By | Revision<br>Date     | Approved<br>By | Approval<br>Date | Description of Change                                                                                                                                                                             |

|-------------------|-------------------|----------------------|----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1               | T. McDermott      | August 8,<br>2019    |                |                  | Original Issue                                                                                                                                                                                    |

| 0.2               | T. McDermott      | November<br>21, 2019 |                |                  | Change 140-pin connector pin definitions, and plug-on-filter pin connectors (4-pin vs. 3-pin connector). Change the ADC and ADC driver chips and datasheet references. Update I2C and SPI tables. |

| 0.2.1             | T. McDermott      | November 22, 2019    |                |                  | Change J5 pin 13 from Ground to +3.3V                                                                                                                                                             |

| 0.3               | T. McDermott      | March 7,<br>2020     |                |                  | Update connector pinout to match actual routed board prototype. Schematic revision XA9. Add jumpers and resistor select descriptions.                                                             |

| 0.4               | T. McDermott      | March 12,<br>2020    |                |                  | Fix date of document on cover page (forgot to change 2019 to 2020 on rev 0.3). Fix typos, add board outline and filter board outline. Complete re-do of J1 from schematic XA10.                   |

| 0.5               | T. McDermott      | April 20,<br>2020    |                |                  | Complete re-do of MEC-140 connector (now J9) and all component references based from schematic XA12.                                                                                              |

| 0.6               | T. McDermott      | November 6,<br>2020  |                |                  | Minor typo corrections of MEC-<br>140 table PP 2.4. XA14<br>schematic is correct, no<br>changes.                                                                                                  |

| 0.7               | T. McDermott      | December<br>18, 2020 |                |                  | Fix typo in document year (was 2010, changed to 2020). Add NSF grant information.                                                                                                                 |

| 1.   | INTRODUCTION                                   | 4  |

|------|------------------------------------------------|----|

| 1.1. | . Scope                                        | 4  |

| 1.2. | Module Summary: RXM-5001D (2-channel receiver) | 4  |

| 1.3. | References                                     | 4  |

| 2.   | ELECTRICAL INTERFACES                          | 5  |

| 2.1. | RF Connectors                                  | 5  |

| 2.2. | Jumpers                                        | 8  |

| 2.3. | Resistor Select (ADC Clock Source)             | 8  |

| 2.4. | Digital and Power Connector                    | 10 |

| 2.5. | I2C and SPI Device Addressing                  | 12 |

| 3.   | MECHANICAL INTERFACES                          | 13 |

| 3.1. | Filter Sub-board                               | 14 |

| 4.   | ACKNOWLEDGMENTS / OTHER INFORMATION            | 16 |

## 1. Introduction

### 1.1. Scope

There are multiple RF Modules that are planned to be defined by TAPR within the TangerineSDR program. Anticipated Modules are:

- TSDR-RXM-5000S Tangerine Receiver Module, single 12-bit 80Msps ADC

- TSDR-RXM-5000D Tangerine Receiver Module, dual 12-bit 80Msps ADC

- TSDR-RXM-5001D Tangerine Receiver Module, dual 14-bit ADC 122.88Msps

- TSDR-TXM-6000 Tangerine Transmitter Module, dual 14-bit DAC 210Msps

- TSDR-TRXM-7000 Tangerine Transceiver 70MHz 6GHz

- TSDR-TRXM-7001 Tangerine Transceiver 10MHz 10GHz

This document applies only to the RXM-5001D Receiver Module.

### 1.2. Module Summary: RXM-5001D (2-channel receiver)

This module uses two 14-bit AD converters, and is intended to support the Personal Space Weather Station (PSWS). It contains requirements in support of PSWS that may or may not exist for other receiver module variants.

The Tangerine SDR Receiver Module RXM-5001D is a dual-channel module that contains two complete receivers, from the antenna connector through the ADC. It receives two radio frequency signals in the 100 kHz to 30 MHz range, optionally filters and attenuates the signals, digitizes the signals with a low-jitter clock, and transfers the digitized samples to the Tangerine SDR Data Engine module.

The unit provides an integrated noise source that can programmatically connect each receiver to a broadband noise source of known amplitude in order to calibrate the receiver sensitivity. The unit uses a single noise source for the two receiver channels, but it will require two relays (one per channel) to select the noise source. It will also contains two plug in RF filters, two programmable attenuators, etc. The noise signal is injected ahead of the attenuator and filter. This provides the ability to capture test data that will allow determination of filter and other characteristics being applied to the received RF signal.

#### 1.3. References

The main configurable component on the receiver is a dual-14-bit ADC device (one ADC per receiver channel), the Analog Devices AD9648. The LTC6420-20 is a dual-channel differential ADC driver with a fixed gain of 20 dB gain.

- AD9648 Datasheet: <a href="https://www.analog.com/media/en/technical-documentation/data-sheets/AD9648.pdf">https://www.analog.com/media/en/technical-documentation/data-sheets/AD9648.pdf</a>

- LVDS Specification: EIA-644. TI (National Semi) App note 971: http://www.ti.com/lit/an/snla165/snla165.pdf

- LTC6420-20 Datasheet: <a href="https://www.analog.com/media/en/technical-documentation/data-sheets/642020fb.pdf">https://www.analog.com/media/en/technical-documentation/data-sheets/642020fb.pdf</a>

### 2. Electrical Interfaces

This section defines the electrical interfaces, jumpers, and resistor-selectable signals of the RF Module, including the connectors, connector pin outs, signals, and signal formats. Control signals are contained on a single MEC connector. External Antenna signals are on SMA connectors. The module is intended to plug onto a TangerineSDR Date Engine and interface to it via the MEC connector.

#### 2.1. RF Connectors

| J1 – Channe<br>Connector ty |                    |                                |                                      |                                                                      |

|-----------------------------|--------------------|--------------------------------|--------------------------------------|----------------------------------------------------------------------|

| Connector<br>Pin #          | Signal<br>Name     | Signal<br>Electrical<br>Format | Input /<br>Output /<br>Bidirectional | Description                                                          |

| 1                           | Receive<br>Antenna | 50 ohm RF<br>Coaxial           |                                      | Input – receives the 0.1 – 30 MHz signal from the channel 1 antenna. |

| J6 – Channe<br>Connector ty |                    |                                |                                      |                                                                      |

|-----------------------------|--------------------|--------------------------------|--------------------------------------|----------------------------------------------------------------------|

| Connector<br>Pin #          | Signal<br>Name     | Signal<br>Electrical<br>Format | Input /<br>Output /<br>Bidirectional | Description                                                          |

| 1                           | Receive<br>Antenna | 50 ohm RF<br>Coaxial           |                                      | Input – receives the 0.1 – 30 MHz signal from the channel 2 antenna. |

| J2 – Channe<br>Connector ty |                   | •                              | oin receptacle    | e strip to hold plug-on RF filter module                                                                                     |

|-----------------------------|-------------------|--------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| Connector<br>Pin #          | Signal<br>Name    | Signal<br>Electrical<br>Format | Input /<br>Output | Description                                                                                                                  |

| 1                           | GND               |                                |                   |                                                                                                                              |

| 2                           | Receive<br>Signal | 50 ohm                         | 0                 | Output from the receiver to the filter input – provides the low level analog 0.1 – 30 MHz signal from the channel 1 antenna. |

| 3                           | Receive<br>Signal | 50 ohm                         | 0                 | Wired in parallel with pin 2                                                                                                 |

| 4                           | GND               |                                |                   |                                                                                                                              |

|                    |                    | Filter Output<br>Inch plug-on p | oin receptacle    | e strip to hold plug-on RF filter module                                                         |

|--------------------|--------------------|---------------------------------|-------------------|--------------------------------------------------------------------------------------------------|

| Connector<br>Pin # | Signal<br>Name     | Signal<br>Electrical<br>Format  | Input /<br>Output | Description                                                                                      |

| 1                  | GND                |                                 |                   |                                                                                                  |

| 2                  | Filtered<br>Signal | 50 ohm                          | I                 | Output from the filter to the receiver input –the low level analog 0.1 – 30 MHz filtered signal. |

| 3                  | Filtered<br>Signal | 50 ohm                          | I                 | Wired in parallel with pin 2                                                                     |

| 4                  | GND                |                                 |                   |                                                                                                  |

| J4 – Channe<br>Connector ty |                   | • • • • • • • • • • • • • • • • • • • | in receptacle     | e strip to hold plug-on RF filter module                                                                                     |

|-----------------------------|-------------------|---------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| Connector<br>Pin #          | Signal<br>Name    | Signal<br>Electrical<br>Format        | Input /<br>Output | Description                                                                                                                  |

| 1                           | GND               |                                       |                   |                                                                                                                              |

| 2                           | Receive<br>Signal | 50 ohm                                | 0                 | Output from the receiver to the filter input – provides the low level analog 0.1 – 30 MHz signal from the channel 1 antenna. |

| 3                           | Receive<br>Signal | 50 ohm                                | 0                 | Wired in parallel with pin 2                                                                                                 |

| 4                           | GND               |                                       |                   |                                                                                                                              |

|                    |                    | Filter Output Inch plug-on p   | oin receptacle    | e strip to hold plug-on RF filter module                                                         |

|--------------------|--------------------|--------------------------------|-------------------|--------------------------------------------------------------------------------------------------|

| Connector<br>Pin # | Signal<br>Name     | Signal<br>Electrical<br>Format | Input /<br>Output | Description                                                                                      |

| 1                  | GND                |                                |                   |                                                                                                  |

| 2                  | Filtered<br>Signal | 50 ohm                         |                   | Output from the filter to the receiver input –the low level analog 0.1 – 30 MHz filtered signal. |

| 3                  | Filtered<br>Signal | 50 ohm                         | I                 | Wired in parallel with pin 2                                                                     |

Description

+3.3 VDC supply voltage to active filter module

| 4 | GND  |  |  |  |

|---|------|--|--|--|

| 7 | CIVE |  |  |  |

### J7 - Channel 1 Receive Filter Power Option

Connector type: 10 x 0.1 Inch plug-on pin receptacle strip to hold plug-on Active RF filter module type (not used for passive RF filter module).

| Connector<br>Pin # | Signal<br>Name  | Signal<br>Electrical<br>Format | Input /<br>Output | Description                                     |

|--------------------|-----------------|--------------------------------|-------------------|-------------------------------------------------|

| 1                  | Analog<br>Gnd 1 |                                |                   | Channel 1 RF Ground                             |

| 2                  | +5 VDC          |                                | 0                 | +5 VDC supply voltage to active filter module   |

| 3                  | Analog<br>Gnd 1 |                                |                   | Channel 1 RF Ground                             |

| 4                  | Digital Gnd     |                                |                   | Common for power supply returns.                |

| 5                  | Analog<br>Gnd 1 |                                |                   | Channel 1 RF Ground                             |

| 6                  | Digital Gnd     |                                |                   | Common for power supply returns.                |

| 7                  | Analog<br>Gnd 1 |                                |                   | Channel 1 RF Ground                             |

| 8                  | +3.3 VDC        |                                | 0                 | +3.3 VDC supply voltage to active filter module |

| 9                  | NC              |                                |                   |                                                 |

| 10                 | NC              |                                |                   |                                                 |

#### J8 - Channel 2 Receive Filter Power Option

Signal

Signal

+3.3 VDC

NC NC

Connector

8

9

10

Connector type: 10 x 0.1 Inch plug-on pin receptacle strip to hold plug-on Active RF filter module type (not used for passive RF filter module).

Input /

Electrical Pin# Name Output **Format** Channel 2 RF Ground 1 Analog Gnd 2 +5 VDC supply voltage to active filter module +5 VDC 0 2 Channel 2 RF Ground 3 Analog Gnd 2 4 Digital Gnd Common for power supply returns. Channel 2 RF Ground 5 Analog Gnd 2 6 Digital Gnd Common for power supply returns. Channel 2 RF Ground Analog Gnd 2

0

#### 2.2. Jumpers

Jumpers are used to select certain options. Some of the jumpers are paralleled with a zero-ohm resistor, which is normally not installed on the board (DNI – Do Not Install). Make sure the zero-ohm resistor is not installed if you wish to open the jumper setting.

#### JP1 - Channel 1 Receive Filter Bypass

Connector type: 2 x 0.1 Inch plug-on pin receptacle.

If Channel 1 does not have a receive filter installed, then insert the jumper to provide signal continuity around the missing filter.

#### JP2 - Channel 2 Receive Filter Bypass

Connector type: 2 x 0.1 Inch plug-on pin receptacle.

If Channel 2 does not have a receive filter installed, then insert the jumper to provide signal continuity around the missing filter.

#### JP4 - Power to noise generator

Connector type: 2 x 0.1 Inch plug-on pin receptacle.

If JP4 is not installed then all power is removed from the noise generator circuitry. Computer control of the noise generator is disabled.

Install JP4 if you wish to be able to use the noise generator, and to turn it on and off under Computer control.

#### JP3 - Channel 1 Receive Ground Bonding

Connector type: 2 x 0.1 Inch plug-on pin receptacle.

Install this jumper to bond the RF common connection of Channel 1 to the system ground if desired or if needed for other reasons.

#### JP5 - Channel 2 Receive Ground Bonding

Connector type: 2 x 0.1 Inch plug-on pin receptacle.

Install this jumper to bond the RF common connection of Channel 2 to the system ground if desired or if needed for other reasons.

# 2.3. Resistor Select (ADC Clock Source)

The ADC clock normally is sourced from the high-performance GPS disciplined clock source. This is enabled by leaving the normally installed zero ohm resistors R45 and R46 intact. If you wish to instead source the ADC clock from the (much lower performance FPGA source) then remove R45 and R46 and instead install zero ohm resistors at R47 and R48 respectively.

|                                        | Use lower performance 122.88 MHz. clock |

|----------------------------------------|-----------------------------------------|

| performance clock module.              | from the FPGA. (for example if no high  |

|                                        | performance clock module is installed). |

| Install zero ohm resistors R45 and R46 | Install zero ohm resistors R47 and R48  |

| Remove zero ohm resistors R47 and R48  | Remove zero ohm resistors R45 and R46   |

# 2.4. Digital and Power Connector

Note that J9 connector pin definitions such as data busses, over-range, and clock out functionality changes dependent on whether the ADC is programmed in CMOS or LVDS DDR mode. The schematic for the module defines both of these cases (read the schematic notes). Which mode is utilized will be decided after testing. LVDS DDR mode requires 245.76 Mbits/sec operation on the data bus pins which may be too fast for the FPGA. However LVDS should reduce the digital noise level.

| NAME                           | LVL       | DIR | Pin# | Pin# | DIR | LVL       | Name     |

|--------------------------------|-----------|-----|------|------|-----|-----------|----------|

| CTRL_SCL                       | 3.3V CMOS | I   | 1    | 2    | -1  | 3.3V CMOS | ID_SCL   |

|                                |           |     | 3    | 4    | I/O | 3.3V CMOS | ID_SDA   |

|                                |           |     | 5    | 6    | I/O | 3.3V CMOS | CTRL_SDA |

|                                |           |     | 7    | 8    |     |           |          |

| +3.3V                          | PWR       |     | 9    | 10   |     | PWR       | 3.3V     |

| GND                            | PWR       |     | 11   | 12   |     | PWR       | GND      |

| UMMY+ (not used in LVDS mode)  | LVDS      | 0   | 13   | 14   | _   | 1.8V CMOS | SYNC     |

| DUMMY+ (not used in LVDS mode) | LVDS      | 0   | 15   | 16   |     |           |          |

| GND                            | PWR       |     | 17   | 18   |     | PWR       | GND      |

| RFM_DOUT0-                     | LVDS      | 0   | 19   | 20   |     |           |          |

| RFM_DOUT0+                     | LVDS      | 0   | 21   | 22   |     |           |          |

| RFM_DOUT1-                     | LVDS      | 0   | 23   | 24   |     |           |          |

| RFM_DOUT1+                     | LVDS      | 0   | 25   | 26   |     |           |          |

| GND                            | PWR       |     | 27   | 28   |     | PWR       | GND      |

| RFM_DOUT2-                     | LVDS      | 0   | 29   | 30   |     |           |          |

| RFM_DOUT2+                     | LVDS      | 0   | 31   | 32   |     |           |          |

| RFM_DOUT3-                     | LVDS      | 0   | 33   | 34   |     |           |          |

| RFM_DOUT3+                     | PWR       |     | 35   | 36   |     |           |          |

| GND                            | PWR       |     | 37   | 38   |     | PWR       | GND      |

| RFM_DOUT4-                     | LVDS      | 0   | 39   | 40   |     |           |          |

| RFM_DOUT4+                     | LVDS      | 0   | 41   | 42   |     |           |          |

| RFM_DOUT5-                     | LVDS      | 0   | 43   | 44   |     |           |          |

| RFM_DOUT5-                     | LVDS      | 0   | 45   | 46   |     |           |          |

| GND                            | PWR       |     | 47   | 48   |     | PWR       | GND      |

| RFM_DOUT6-+                    | LVDS      | 0   | 49   | 50   |     |           |          |

| RFM_DOUT6+                     | LVDS      | 0   | 51   | 52   |     |           |          |

| RFM_DOUT7-                     | LVDS      | 0   | 53   | 54   |     |           |          |

| RFM_OUT7+                      | LVDS      | 0   | 55   | 56   |     | DW:-      | 21.12    |

| GND                            | PWR       | 0   | 57   | 58   |     | PWR       | GND      |

|                                |           |     |      |      |     |           |          |

60

62

61

LVDS

LVDS

RFM\_DOUT8-

RFM\_DOUT8+

| RFM_DOUT9-      | LVDS      | 0   | 63  | 64  |     |      |              |

|-----------------|-----------|-----|-----|-----|-----|------|--------------|

| RFM_OUT9+       | LVDS      | 0   | 65  | 66  |     |      |              |

| RFM_DOUT10-     | LVDS      | 0   | 67  | 68  |     |      |              |

| RFM_DOUT10+     | LVDS      | 0   | 69  | 70  |     |      |              |

| GND             | PWR       |     | 71  | 72  |     | PWR  | GND          |

| OSC_CLK_IN+     | LVDS      | - 1 | 73  | 74  | -1  | LVDS | FPGA_CLK_IN- |

| OSC_CLK_IN-     | LVDS      |     | 75  | 76  | - 1 | LVDS | FPGA_CLK_IN+ |

| DAT_CLK_OUT0-   | LVDS      | 0   | 77  | 78  |     |      |              |

| DAT_CLK_OUT0+   | LVDS      | 0   | 79  | 80  |     |      |              |

| GND             | PWR       |     | 81  | 82  |     | PWR  | GND          |

| RFM_DOUT11-     | LVDS      | 0   | 83  | 84  |     |      |              |

| RFM_DOUT11+     | LVDS      | 0   | 85  | 86  |     |      |              |

| RFM_DOUT12-     | LVDS      | 0   | 87  | 88  |     |      |              |

| RFM_DOUT12+     | LVDS      | 0   | 89  | 90  |     |      |              |

| RFM_DOUT13-     | LVDS      | 0   | 91  | 92  |     |      |              |

| RFM_DOUT13-     | LVDS      | 0   | 93  | 94  |     |      |              |

| GND             | PWR       |     | 95  | 96  |     | PWR  | GND          |

| RFM_OVF-        | LVDS      | 0   | 97  | 98  |     |      |              |

| RFM_OVF+        | LVDS      | 0   | 99  | 100 |     |      |              |

|                 |           |     | 101 | 102 |     |      |              |

|                 |           |     | 103 | 104 |     |      |              |

| SPI_BIDIR_1.8V  | 1.8V CMOS | I/O | 105 | 106 |     |      |              |

| SPI_SCLK_1.8V   | 1.8V CMOS | _   | 107 | 108 |     |      |              |

| SPI_CSEL_F_1.8V | 1.8V CMOS | _   | 109 | 110 |     |      |              |

|                 |           |     | 111 | 112 |     |      |              |

| GND             | PWR       |     | 113 | 114 |     | PWR  | GND          |

|                 |           |     | 115 | 116 |     |      |              |

|                 |           |     | 117 | 118 |     |      |              |

|                 |           |     | 119 | 120 |     |      |              |

|                 |           |     | 121 | 122 |     |      |              |

| GND             | PWR       |     | 123 | 124 |     | PWR  | GND          |

|                 |           |     | 125 | 126 |     |      |              |

|                 |           |     | 127 | 128 |     |      |              |

|                 |           |     | 129 | 130 |     |      |              |

|                 |           |     | 131 | 132 |     |      |              |

|                 |           |     | 133 | 134 |     |      |              |

|                 |           |     | 135 | 136 |     |      |              |

| +1.8V           | PWR       |     | 137 | 138 |     | PWR  | +5V          |

| +5V             | PWR       |     | 139 | 140 |     | PWR  | +12V         |

Note in the table below that the Blue and Yellow color directions are reversed compared to the data engine table. A unidirectional output from the RFM is a unidirectional input to the DE, and vice versa. Reversing the colors makes matching data busses the same color on both modules.

| Pin Group | Direction | Alt Function |

|-----------|-----------|--------------|

|           |           |              |

| Power                  | Fixed                  | none                   |

|------------------------|------------------------|------------------------|

| CLKIN                  | Differential LVDS in   | Single Ended clock in  |

| CLKOUT                 | Differential LVDS out  | Single ended in or out |

| Serial Command         | Fixed or I/O           | none                   |

| DOUT0/DOUT1            | Differential LVDS out  | Single Ended in or out |

| DIN                    | Differential LVDS in   | Single Ended in or out |

| Serial Command 1.8V or | Input, Output, and I/O |                        |

| CMOS control 1.8V      |                        |                        |

| Pin not connected      |                        |                        |

# 2.5. I2C and SPI Device Addressing

All RF modules implement an Identification EPROM that allows the FPGA on the Data Engine to configure the I/O signals to match the module type plugged in (within FPGA capability limits). The Identification EPROM is connected separately from other I2C devices.

| Device             | I2C Address | Chip Select                         |

|--------------------|-------------|-------------------------------------|

| I2C Identification | -           | CS not used (EPROM always selected) |

| EPROM              |             |                                     |

The RXM-5100D implements a control interface consisting of an octal latch to drive the relays and two status LEDs. These occur of different I2C pins than the EPROM I2C.

| Device         | I2C Address                             | Chip Select                       |  |

|----------------|-----------------------------------------|-----------------------------------|--|

| Control Output | 000                                     | CS not used (Control latch always |  |

| Register       |                                         | selected)                         |  |

| Bit 0          | Low = Channel 1 Noise Relay Enable      |                                   |  |

| Bit 1          | Low = Channel 1 10 dB attenuator enable |                                   |  |

| Bit 2          | Low = Channel 1 20 dB attenuator enable |                                   |  |

| Bit 3          | Low = Channel 2 Noise Relay Enable      |                                   |  |

| Bit 4          | Low = Channel 2 10 dB attenuator enable |                                   |  |

| Bit 5          | Low = Channel 2 20 dB attenuator enable |                                   |  |

| Bit 6          | Low = Turn on Green status LED          |                                   |  |

| Bit 7          | Low = Turn on Red status LED            |                                   |  |

The AD9648 ADC uses a 3-wire SPI interface. The data line is bidirectional rather than the traditional MISO and MOSI lines used in SPI.

| Device              | SPI Address | Chip Select         |

|---------------------|-------------|---------------------|

| AD9648 Dual-channel | -           | CSEL = 0 to enable. |

| ADC                 |             | CSEL needs to be    |

| toggled to update |

|-------------------|

| some modes.       |

# 3. Mechanical Interfaces

Note that the reference designators on the figures below are wrong. These drawings are only for mechanical placement and dimensioning. This section describes the mechanical packaging of the clock module, including board profile, mounting and screw holes, and connector placement.

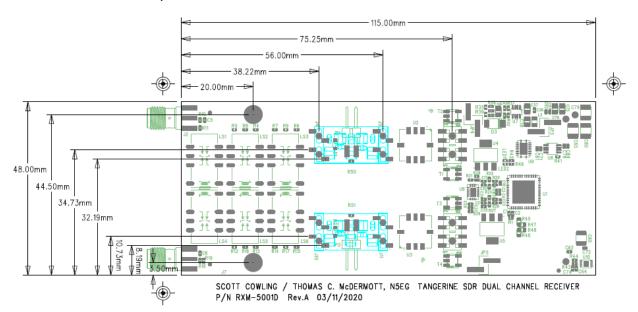

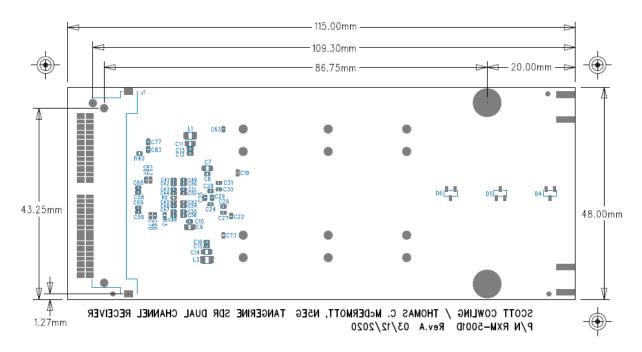

#### Figure 3 – Receiver Outline

The receiver module profile is shown in Figure 3. The Main electrical connector type is SamTec MEC 140 pin, 0.5mm spacing on the rear side.. The module mounts to the PSWS Data Engine using two #4-40 screws at the locations shown in the drawing (20 mm from the RF connector end of the module).

#### 3.1. Filter Sub-board

Each receiver channel may be independently fitted with a filter sub-board. A filter sub-board can be either passive or active. The passive board utilizes two connectors, while the active board utilizes 3 connectors, according to the table below.

| Filter type   | Channel 1 Connectors                | Channel 2 Connectors                 |

|---------------|-------------------------------------|--------------------------------------|

| Passive       | J2 – output from receiver to filter | J10 – output from receiver to filter |

| filter sub-   | input                               | input                                |

| board         | J3 – receiver input from filter     | J11 – receiver input from filter     |

|               | output                              | output                               |

| Active filter | J2 – output from receiver to filter | J10 – output from receiver to filter |

| sub-board     | input                               | input                                |

|               | J3 – receiver input from filter     | J11 – receiver input from filter     |

|               | output                              | output                               |

|               | J7 – power & power return to        | J8 – power & power return to filter  |

|               | filter                              |                                      |

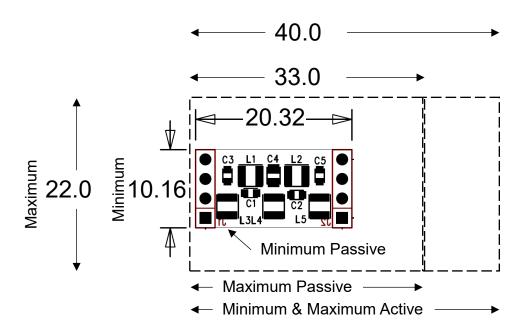

The filter dimensions for the minimum passive, maximum passive, and maximum active filter sub-board are shown in Figure 3.1a. Dimensions are in mm. The table shows the module minimum and maximum dimensions.

**Figure 3.1a Filter Dimensions**

| Filter type          | Minimum Size        | Maximum Size      |

|----------------------|---------------------|-------------------|

| Passive              | 10.16 mm x 20.32 mm | 22.0 mm x 33.0 mm |

| filter sub-          |                     |                   |

| board                |                     |                   |

| <b>Active filter</b> | 10.16 mm x 40.0 mm  | 22.0 mm x 40.0 mm |

| sub-board            |                     |                   |

The Active filter is longer to accommodate the third (power) connector.

# 4. Acknowledgments / Other Information

We would like to thank the National Science Foundation (NSF) for support of the Personal Space Weather Station project from the following grants:

- NSF AGS-2002278 (Scranton, NJIT, TangerineSDR, Magnetometer)

- NSF AGS-1932972 (Alabama Software and Database)

- NSF AGS-1932997 (CWRU Low Cost PSWS)