# TangerineSDR

Clock Module (CKM)

## **Interface Control Document**

Version Number: 0.3 Version Date: August 13, 2019 Document Number: TSDR-CKM-ICD

# **VERSION HISTORY**

| Version<br>Number | Implemented<br>By | Revision<br>Date   | Approved<br>By | Approval<br>Date | Description of<br>Change                                                               |

|-------------------|-------------------|--------------------|----------------|------------------|----------------------------------------------------------------------------------------|

| 0.1               | T. McDermott      | July 10, 2019      |                |                  | Original Issue.                                                                        |

| 0.2               | T. McDermott      | July 12, 2019      |                |                  | Separate out GPS antenna<br>and Ext Clock Ref. to separate<br>connectors J1, J2 (SMA). |

| 0.2.1             | T. McDermott      | August 1,<br>2019  |                |                  | Reformat and Change<br>Document Number                                                 |

| 0.3               | T. McDermott      | August 13,<br>2019 |                |                  | Change/add pins on M.2<br>connector J3. Reformat J3<br>table.                          |

|                   |                   |                    |                |                  |                                                                                        |

|                   |                   |                    |                |                  |                                                                                        |

| 1.  | INTRODUCTION          | 4 |

|-----|-----------------------|---|

| 1.1 | . References          | 4 |

| 1.2 | . GPS Receiver        | 4 |

| 1.3 | . Synthesizer         | 5 |

| 2.  | ELECTRICAL INTERFACES | 5 |

| 3.  | MECHANICAL INTERFACES | 7 |

### 1. Introduction

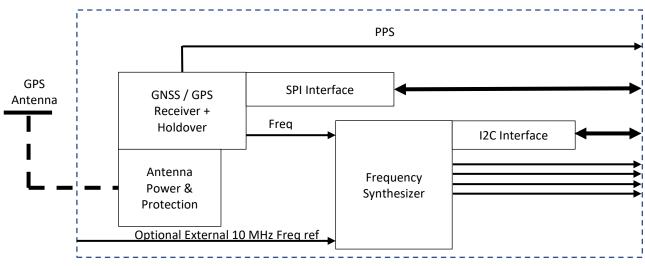

The Personal Space Weather Station (PSWS) Clock Module provides GPS derived time and frequency for input to the PSWS TangerineSDR receiver Data Engine (DE). It is a low cost module that provides a high accuracy pulse-per-second (PPS) timing strobe, high-accuracy UTC time, and programmable frequency synthesizer outputs derived from a GPS disciplined oscillator. The four synthesizer outputs have phase noise performance that meets the needs of the PSWS receiver. The module is intended to be programmed from the DE, and to provide timing and frequency signals to the DE. Figure 1 is a block diagram of the Clock Module.

Figure 1. Block Diagram of Clock Module

The clock module contains a holdover oscillator which continues the phase and frequency outputs when GPS receiver signal is lost. It uses a low-phase-noise oscillator with frequency stability correction. The holdover oscillator may be integrated within the GPS receiver, or it may be outside the receiver but contained on the module.

#### 1.1. References

The PSWS Clock Module Specification describes the purpose, use cases, functionality and performance requirements for the clock module.

#### 1.2. GPS Receiver

The GPS receiver registers, block diagrams, and control / status maps are available from the manufacturer programming document. While the exact GPS module choice is still TBD, a representative module would be the u-blox LEA-M8F.

• All Documentation located at:

https://www.u-blox.com/en/product/lea-m8f-module#tab-documentation-resources

- Datasheet: UBX-14001772

- Hardware Integration Manual: UBX-14000034

- System Integration Guide: UBX-14001603

- Receiver Description + Protocol Specification: UBX-13003221

#### 1.3. Synthesizer

The Synthesizer registers, block diagrams, and control / status maps are available from the manufacturer programming document. While the exact Synthesizer choice is still TBD, a representative choice would be the Silicon Labs SI-5344 D.

- The documentation is not centrally collected, individual links are needed.

- Evaluation Board User's Guide: <u>https://www.silabs.com/documents/public/user-guides/Si5344-D-EVB.pdf</u>

- Datasheet: <u>https://www.silabs.com/documents/public/data-sheets/Si5345-44-42-</u> D-DataSheet.pdf

- Reference Manual: <u>https://www.silabs.com/documents/public/reference-manuals/Si5345-44-42-D-RM.pdf</u>

## 2. Electrical Interfaces

This section defines the electrical interfaces of the Clock Module, including the connectors, connector pin outs, signals, and signal formats. Control signals are contained on a single M.2 connector. GPS and External Ref Clock signals are on SMA connectors. The module has two intended uses:

- 1. Plug onto a Tangerine SDR Data Engine board using the M.2 connector.

- 2. Independent use by plugging onto a breakout board which routes the M.2 connector to various connectors for SPI, I2C, and Synthesizer outputs.

| J1 - GPS Receive Antenna + DC Power to Antenna<br>Connector type: SMA Receptacle |                |                                                 |                                      |                                                                                                                                                          |  |  |  |

|----------------------------------------------------------------------------------|----------------|-------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Connector<br>Pin #                                                               | Signal<br>Name | Signal<br>Electrical<br>Format                  | Input /<br>Output /<br>Bidirectional | Description                                                                                                                                              |  |  |  |

| 1                                                                                | GPS<br>Antenna | 50 ohm RF<br>Coaxial also<br>supplying<br>power |                                      | Output - Provides current-limited DC power<br>(+3.3VDC or +5VDC TBD) to the GPS antenna.<br>Input – receives the 1.5 GHz GPS signal from<br>the antenna. |  |  |  |

| J2 – External 10 MHz Reference Clock Input<br>Connector type: SMA Receptacle |                                 |                      |  |                                                                                 |  |  |  |

|------------------------------------------------------------------------------|---------------------------------|----------------------|--|---------------------------------------------------------------------------------|--|--|--|

| Connector<br>Pin #                                                           |                                 |                      |  |                                                                                 |  |  |  |

| 1                                                                            | External 10<br>MHz<br>Reference | 50 ohm RF<br>Coaxial |  | Input – Receives Optional External 10 MHz reference inputs. Terminated 50 ohms. |  |  |  |

| J3 – GPS and Synthesizer Control and Status, PPS and Synthesizer Outputs                           |           |     |       |       |     |           |                      |

|----------------------------------------------------------------------------------------------------|-----------|-----|-------|-------|-----|-----------|----------------------|

| Connector type: M.2 – M-Keyed                                                                      |           |     |       |       |     |           |                      |

| Note the Pins numbers are WRONG and arbitrary at this time.                                        |           |     |       |       |     |           |                      |

| The Exact pin layout will need to await the ICD for the Data Engine and analysis to prevent module |           |     |       |       |     |           |                      |

| interchangeability and potential power mis-supply problems.                                        |           |     |       |       |     |           |                      |

| NAME                                                                                               | LVL       | DIR | Pin # | Pin # | DIR | LVL       | Name                 |

| GND                                                                                                | PWR       |     | 1     | 2     | I   | 3.3V CMOS | IDENT_I2C_CLK        |

| CLKM_PPS_OUT+                                                                                      | LVDS      |     | 3     | 4     | I/O | 3.3V CMOS | IDENT_I2C_DAT        |

| CLKM_PPS_OUT-                                                                                      | LVDS      | I   | 5     | 6     | I   | 3.3V CMOS | SPI_MOSI             |

| GND                                                                                                | PWR       |     | 7     | 8     | 0   | 3.3V CMOS | SPI_MISO             |

| SYN_I2C_CLK                                                                                        | 3.3V CMOS | I   | 9     | 10    | - I | 3.3V CMOS | SPI_CLK              |

| SYN_I2C_DAT                                                                                        | 3.3V CMOS | I   | 11    | 12    | - I | 3.3V CMOS | SPI_SS               |

| SYN_I2C_CS0n                                                                                       | 3.3V CMOS | I   | 13    | 14    | - I | 3.3V CMOS | Unused_I2C_CS1n      |

| GND                                                                                                | PWR       |     | 15    | 16    |     | PWR       | GND                  |

| CLKM_SYN_OUT0+                                                                                     | LVDS      | 0   | 17    | 18    |     | LVDS      | Unused_CLKM_SYN_IN0+ |

| CLKM_SYN_OUT0-                                                                                     | LVDS      | 0   | 19    | 20    |     | LVDS      | Unused_CLKM_SYN_IN0- |

| GND                                                                                                | PWR       |     | 21    | 22    |     | PWR       | GND                  |

| CLKM_SYN_OUT1+                                                                                     | LVDS      | 0   | 23    | 24    | -   | LVDS      | Unused_CLKM_SYN_IN1+ |

| CLKM_SYN_OUT1-                                                                                     | LVDS      | 0   | 25    | 26    |     | LVDS      | Unused_CLKM_SYN_IN1- |

| GND                                                                                                | PWR       |     | 27    | 28    |     | PWR       | GND                  |

| CLKM_SYN_OUT2+                                                                                     | LVDS      | 0   | 29    | 30    | -   | LVDS      | Unused_CLKM_SYN_IN2+ |

| CLKM_SYN_OUT2-                                                                                     | LVDS      | 0   | 31    | 32    |     | LVDS      | Unused_CLKM_SYN_IN2- |

| GND                                                                                                | PWR       |     | 33    | 34    |     | PWR       | GND                  |

| CLKM_SYN_OUT3+                                                                                     | LVDS      | 0   | 35    | 36    | -   | LVDS      | Unused_CLKM_SYN_IN3+ |

| CLKM_SYN_OUT3-                                                                                     | LVDS      | 0   | 37    | 38    | - I | LVDS      | Unused_CLKM_SYN_IN3- |

| GND                                                                                                | PWR       |     | 39    | 40    |     | PWR       | GND                  |

| CLKM_STAT_OUT0+                                                                                    | LVDS      | 0   | 41    | 42    | 0   | LVDS      | CLKM_STAT_OUT1+      |

| CLKM_STAT_OUT0-                                                                                    | LVDS      | 0   | 43    | 44    | 0   | LVDS      | CLKM_STAT_OUT1+      |

| GND                                                                                                | PWR       |     | 45    | 46    |     | PWR       | GND                  |

| 1.8V                                                                                               | PWR       |     | 47    | 48    |     | PWR       | 1.8V                 |

| 3.3V                                                                                               | PWR       |     | 49    | 50    |     | PWR       | 3.3V                 |

| 5V                                                                                                 | PWR       |     | 51    | 52    |     | PWR       | 5V                   |

| 12V                                                                                                | PWR       |     | 53    | 54    |     | PWR       | 12V                  |

| Unused_CLKM_GPIO_0                                                                                 | 3.3V CMOS |     | 55    | 56    |     | 3.3V CMOS | Unused_CLKM_GPIO_1   |

| Unused_CLKM_GPIO_2                                                                                 | 3.3V CMOS |     | 57    | 58    |     | KEY_M     |                      |

|                                                                                                    | KEY_M     |     | 59    | 60    |     | KEY_M     |                      |

|            | KEY_M<br>KEY_M | 61<br>63 | 62<br>64 | KEY_M<br>KEY_M |            |

|------------|----------------|----------|----------|----------------|------------|

|            | KEY_M          | 65       | 66       | KET_M<br>KEY_M |            |

| Unassigned |                | 67       | 68       |                | Unassigned |

| Unassigned |                | 69       | 70       |                | Unassigned |

| Unassigned |                | 71       | 72       |                | Unassigned |

| Unassigned |                | 73       | 74       |                | Unassigned |

| Unassigned |                | 75       |          | •              |            |

Note in the table below that the Blue and Yellow color directions are reversed compared to the data engine table. A unidirectional output from the RFM is a unidirectional input to the DE, and vice versa. Reversing the colors makes matching data busses the same color on both modules.

| Pin Group      | Direction             | Alt Function           |

|----------------|-----------------------|------------------------|

| Power          | Fixed                 | none                   |

| CLKIN          | Differential LVDS in  | Single Ended clock in  |

| CLKOUT         | Differential LVDS out | Single ended in or out |

| Serial Command | Fixed or I/O          | none                   |

| DOUT0/DOUT1    | Differential LVDS out | Single Ended in or out |

| DIN            | Differential LVDS in  | Single Ended in or out |

| GPIO           | Fixed or I/O          | none                   |

| Connector Key  |                       |                        |

#### **3. Mechanical Interfaces**

This section describes the mechanical packaging of the clock module, including board profile, mounting and screw holes, and connector placement.

The module profile is shown in Figure 3.1. TBD. The module dimensions are TBD.

The Main electrical connector type is TBD (might be M.2?). The module mounts to the PSWS Data Engine as shown in figure 3.2 using a TBD screw at the locations shown in the profile drawing.